Den 68000er unter die Lupe genommen

Um es gleich am Anfang zu sagen, ein so leistungsfähiger Prozessor wie der 68000er ist unmöglich mit allen Merkmalen und Details auf ein paar Seiten zu beschreiben. Deswegen wird in diesem Artikel versucht, nur auf das einzugehen, was uns am wichtigsten erschien.

Zur Geschichte des 68000er

Die Entwicklung des 68000er begann im Jahre 1977 im MOS-Entwicklungszentrum der Firma MOTOROLA EMC. Dort wollte man einen leistungsfähigen Prozessor für die achtziger Jahre schaffen. Er sollte eine Familienarchitektur aufweisen, damit man ihn — je nach dem neuesten Stand der Technik — erweitern kann. Er sollte möglichst einfach, aber effektiv zu programmieren sein. Ferner sollte er universell einsetzbar sein und höhere Programmiersprachen unterstützen. Der Prototyp kam dann 1979 auf den Markt. Mit ihm war es gelungen, eine Vielzahl von Vorzügen auf einem Chip zu vereinigen, auf die wir auf den folgenden Seiten näher eingehen wollen.

Datenformate

Auch auf die Gefahr hin, daß viele jetzt gequält aufstöhnen, kommt man nicht darum herum, doch zuerst einmal kurz die vom 68 000er verwendeten Datenformate zu erklären. Da Computer intern mit einer zweiwertigen Logik arbeiten, stellt das Binary Digit (”0” oder ”1”), kurz Bit genannt, die kleinste zu verarbeitende Einheit dar. Die nächst größere Einheit ist das sogenannte Nibble. Es besteht aus vier Bit und wird beim Gebrauch von binär kodierten Dezimaldaten (BCD) benutzt. Acht Bit bilden wiederum ein Byte. Die Standard-Datenform beim 68 000er ist, da er ein 16-Bit-Prozessor ist, das Wort. Es besteht, wie sich leicht vermuten läßt, aus 16 Bit. Es lassen sich jedoch auch 32 Bit auf einmal verarbeiten. In diesem Falle spricht man von einem Langwort.

Es sei noch gesagt, daß Zugriffe auf Worte und Langworte nur von geraden Adressen erfolgen dürfen. Wird diese Bedingung nicht erfüllt, wird eine sogenannte Ausnahmebehandlung (Exception) ausgeführt.

Die Anschlußbelegung

Der Prozessor hat 64 Anschlüsse, die man in neun Gruppen einteilen kann. (Eine Abbildung der Anschlußbelegung kann man im nebenstehenden Fenster sehen.) Die erste Gruppe besteht aus den 16 Datenleitungen (DO - D15), auf denen die Daten byte-oder wortweise übertragen werden.

Die zweite Gruppe besteht aus den 23 Adreßleitungen (Al - A 23). Auf ihnen werden die Adressen, die von dem Prozessor erzeugt wurden und zur Auswahl einer der Speicherstellen dienen, transportiert. Diese Adressen legen Quelle und Ziel der über den Datenbus laufenden Daten fest. Mit den 23 Adreßleitungen wäre sogar eine direkte Adressierung von bis zu 16 MByte möglich. Daran ist allerdings beim ST nicht zu denken, da die übrige Hardware dies nicht zuläßt.

Uber die Adresse AO ist zu sagen, daß sie nicht nach außen geführt ist, im Chip selbst aber natürlich existiert. Sie ist hinter den beiden Signalen Upper Date Strobe (Oberes Daten-Strobe, UDS) und Lower Date Strobe (Unteres Daten-Strobe, LDS) verborgen, womit wir bei der nächsten Gruppe wären. Diese dienen mit den Signalen Adreß-Strobe (AS), DaTa ACKnow-ledge (Datenquittierung, DTACK) und den Read/Write (Lese-/Schreibsignal, R/W) der asynchronen Bussteuerung, durch die der Speicher und die 16-Bit-Peripherie angeschlossen werden.

Das Signal Adreß-Strobe zeigt an, daß sich eine gültige Adresse auf dem Adreßbus befindet. Erkennt der 68 000er während eines Lesezykluses Data-Acknowledge, werden die betreffenden Daten, die sich auf dem Datenbus befinden, übernommen. Durch das Read/Write-Signal wird bestimmt, ob die Datenübertragung ein Lese- oder Schreibvorgang ist. Ferner wird, zusammen mit beiden Daten-Strobes festgelegt, ob die obere (Bits 0-7) oder die untere (Bits 8-15) angesprochen werden (siehe Tabelle 1).

Gruppe vier beinhaltet die Signale, die mit der Busverwaltung zu tun haben. Es sind Bus Request (Busanforderung, BR), Bus Grant (Buszuteilung, BG) und Bus Grant Acknowledge (Buszuteilungsquittierung, BGACK).

Durch Bus Request wird dem Prozessor mitgeteilt, daß eine Peripherie-Einheit den Bus benutzen will. Bus Grant zeigt allen anderen Busbenutzern an, daß der Prozessor nach Beendigung des derzeitigen Zykluses die Bussteuerung abgibt. Durch Bus Grant Acknowledge wird erkannt, daß eine andere Einheit die Bussteuerung übernommen hat. Dazu müssen aber zuvor die Signale AS, DTACK und BGACK inaktiv und BG aktiv werden.

Die drei Interrupt Priority Line-Signale (IPLO - LPL2) bilden die fünfte Gruppe. Durch sie werden die einzelnen Interrupt-Ebenen (zusammen sieben Möglichkeiten) bestimmt, auf die wir noch näher bei der Exceptionbesprechung eingehen wollen. Es sei nur gesagt, daß dem Anwender insgesamt 199 Interruptvektoren zur Verfügung stehen.

Die nächste Gruppe bilden die sogenannten Function Code Signale (FCO - FC1). Diese zeigen in kodierter Form den momentanen Status und die des gerade ausgeführten Zykluses an (siehe Tabelle 2). Die Signale sind immer dann gültig, wenn das Adreß-Strobe-Signal aktiv ist. Zu dem Unterschied zwischen User- und Supervisor-Modus kommen wir noch bei der Besprechung der Register.

Die siebte Gruppe mit den Signalen VPA, E und VMA dienen zur synchronen Bussteuerung. Das Valid Periphal Adress-Signal (Gültige Peripherieadresse, VPA) zeigt an, daß die Datenübertragung mit dem Freigabe-Signal Enable (E) synchronisiert werden muß. Außerdem gibt es an, daß das betreffende Peripheriegerät über einen synchronen Bus verfügt. Das Valid Memory Adress-Signal (Gültige Speicheradresse) meldet, daß der Prozessor synchronisiert ist und sich eine gültige Adresse auf dem Adreßbus befindet.

Die vorletzte Gruppe bilden die Systemsteuerungs-Signale. Sie unterschieden sich in BERR, RESET und HALT. Das Bus ERRor-Signal (Busfehler, BERR) kann durch mehrere Fehlerarten ausgelöst werden. Einmal kann eine Peripherieeinheit nicht antworten oder es kann zum Beispiel eine falsche Interrupt-Prozedur erfolgt sein. Wird BERR LOW, so wird eine Ausnahmebehandlung (Exception) eingeleitet. Falls auch noch das HALT-Signal LOW wird, versucht der Prozessor den Befehl, der den Busfehler ausgelöst hat, zu wiederholen. Klappt auch dieser Versuch nicht, tritt ein sogenannter doppelter Busfehler auf und der Prozessor wird angehalten.

| UDS | LDS | R | w | D8 - D15 | DO - D7 |

| 1 | 1 | — | — | keine gült. Daten | keine gült. Daten |

| 0 | 0 | 1 | 0 | Datenbits 8 — 15 | Datenbits 0 — 7 |

| 1 | 0 | 1 | 0 | keine gült. Daten | Datenbits 0-7 |

| 0 | 1 | 1 | 0 | Datenbits 8—15 | keine gült. Daten |

| 0 | 0 | 0 | 1 | Datenbits 8-15 | Datenbits 0-7 |

| 1 | 0 | 0 | 1 | Datenbits 8-15 | Datenbits 0-7 |

| 0 | 1 | 0 | 1 | Datenbits 8-15 | Datenbits 0-7 |

Tabelle 1: Datenbussteuerung mit den Signalen UDS, LDS und R/W.

| FCO | FC1 | FC2 | Status |

| 0 | 0 | 0 | Undefiniert |

| 0 | 0 | 1 | Daten im User-Modus |

| 0 | 1 | 0 | Programm im User-Modus |

| 0 | 1 | 1 | Undefiniert |

| 1 | 0 | 0 | Undefiniert |

| 1 | 0 | 1 | Daten im Supervisor-Modus |

| 1 | 1 | 0 | Programm im Supervisor-Modus |

| 1 | 1 | 1 | Interruptquittierung |

Tabelle 2: Statusmeldungen durch die Signale FCO - FC 2.

Man sollte eigentlich meinen, daß der Begriff RESET jedem Computer-Anwender geläufig ist. Doch beim 68 000er gibt es noch einiges dazu zu sagen. Durch einen externen RESET (zum Beispiel mittels des RESET-Knopfes) werden der Prozessor und die ganze Peripherie in ihren Einschaltzustand versetzt. Nun ist bei diesem Prozessor auch noch ein durch Software erzeugter, interner RESET möglich. Durch ihn werden lediglich die externen Peripherie-Einheiten zurückgesetzt. Um dies zu erreichen, gibt es den Assemblerbefehl RESET.

Die letzte Gruppe von Anschlüssen ist an jedem Prozessor vorhanden. E ist das CLocK-Signal (Takt, CLK), die Spannungsversorgung Vcc und die Massezuleitung GND. Die Taktfrequenz des Prozessors beträgt beim ATARI ST 8 1MHz.

Ausnahmebehandlungen (Exceptions)

Exceptions sind durch aufgetretene Fehler oder interne Befehle ausgelöste Ausnahmebehandlungen. Zu ihnen zählen auch die Interrupts und Traps, auf die wir gleich noch kommen. Jeder Exception ist ein bestimmter Exception-Vektor mit eigener Vektornummer zugeordnet. Für diese Vektoren sind die Adressen $000 - $3FC im Arbeitsspeicher vorgesehen (siehe Tabelle ). Beim Eintreten einer Exception holt sich der Prozessor automatisch den Inhalt der Adresse, die im betreffenden Vektor steht, in den Programmzähler. Dazu sei noch erwähnt, daß so die "Pilze” bzw. "Bomben” beim Absturz des Systems entstehen. Die Anzahl dieser Symbole gibt nämlich die Vektornummer des Fehlers an, der diese Ausnahmebehandlung ausgelöst hat.

Die einzelnen Vektoren haben folgende Bedeutung:

Der RESET (SSP)-Vektor beinhaltet die Adresse, deren Inhalt nach einem Hardware-RESET in den Supervisor-Stackpointer geladen wird.

Im RESET (PC)-Vektor steht die Adresse, deren Inhalt nach einem Hardware-RESET in den Programmzähler geladen wird.

Auf den Busfehler sind wir ja schon vorher kurz eingegangen. Er wird immer von einem externen Gerät ausgelöst.

Ein Adreßfehler tritt dann auf, wenn bei einer Wort- oder Langwortverarbeitung der Zugriff auf eine ungerade Adresse stattfindet.

Belegung der Ausnahmevektoren beim ATARI ST

| Vektor nummer | Adresse hex | Zuordnung | |||

| 0 | 000 | Anfangsadresse SSP nach Reset | |||

| 1 | 004 | Anfangsadresse PC nach Reset | |||

| 2 | 008 | Busfehler | |||

| 3 | OOC | Adreßfehler | |||

| 4 | 010 | unzulässiger Befehl | |||

| 5 | 014 | Division durch Null | |||

| 6 | 018 | Befehl CHK | |||

| 7 | 01C | Befehl TRAPV | |||

| 8 | 020 | Pr ivilegverletzung | |||

| 9 | 024 | Trace | |||

| 10 | 028 | 1010 Emulator (Line | A) | ||

| 11 | 02C | 1111 Emulator (Line | F) | ||

| 12 | 030 | reserv iert | |||

| 13 | 034 | reserv iert | |||

| 14 | 038 | reserv iert | |||

| 15 | 03C | nicht initialisierter Int.- | Vektor | ||

| 16 | - 23 | 040 - | 05C reserviert | ||

| 24 | 060 | Unechter Interrupt | |||

| 25 | 064 | Interrupt-Autovektor | (Ebene | 1) | |

| 26 | 068 | Interrupt-Autovektor | (Ebene | 2) | |

| 27 | 06 C | Interrupt-Autovektor | (Ebene | 3) | |

| 28 | 070 | Interrupt-Autovektor | (Ebene | 4) | |

| 29 | 074 | Interrupt-Autovektor | (Ebene | 5) | |

| 30 | 078 | Interrupt-Autovektor | (Ebene | 6) | |

| 31 | 07C | Interrupt-Autovektor | (Ebene | 7) | |

| 32 | 080 | TRAP 0 | |||

| 33 | 08 4 | TRAP 1 (GEMDOS) | |||

| 34 | 088 | TRAP 2 (GEM) | |||

| 35 | 08C | TRAP 3 | |||

| 36 | 090 | TRAP 4 | |||

| 37 | 094 | TRAP 5 | |||

| 38 | 098 | TRAP 6 | |||

| 39 | 09C | TRAP 7 | |||

| 40 | 0A0 | TRAP 8 | |||

| 41 | 0A4 | TRAP 9 | |||

| 42 | 0A8 | TRAP 10 | |||

| 43 | OAC | TRAP 11 | |||

| 44 | 0B0 | TRAP 12 | |||

| 45 | OB 4 | TRAP 13 (BIOS) | |||

| 46 | 0B8 | TRAP 14 (XBIOS) | |||

| 47 | OBC | TRAP 15 | |||

| 48 | - 63 | oco - | OFC reserviert | ||

| 64 | - 255 | 100 - | 3FC Non-Interrupt-Autovektoren | ||

Unter einem unzulässigen Befehl versteht man eine Bitkombination, die nicht vom Prozessor entschlüsselt werden kann. Dies kann man zum Beispiel zum Setzen von Breakpoints nutzen. Der Assemblerbefehl ILLEGAL hat einen unzulässigen Befehl zur Folge.

Division durch Null erklärt sich an und für sich von selbst. Wenn bei einer Division im Nenner eine Null steht, ist dies ein mathematischer Fehler und hat eine Exceptionabarbeitung zur Folge.

Durch den Befehl CHK werden die Register auf ihre Grenzen geprüft. Befindet sich der Prozessor außerhalb des definierten Bereichs, so wird dieser CHK-Vektor benutzt.

Das TRAPV-Vektor tritt dann in Kraft, wenn das Overflow-Flag im Statusregister gesetzt ist und der Befehl TRAPV gerade ausgeführt wird.

Eine Privilegverletzung kommt dann vor, wenn ein Anwender einen privilegierten Befehl (zum Beispiel MO VE to SR) ablaufen läßt, sich aber noch im User-Modus befindet.

Ist das Trace-Flag im Statusregister gesetzt, wird nach jedem Befehl in das mit dem Trace-Vektor bestimmte Programm gesprungen. So ist eine Einzelschritt-Bearbeitung eines Programms relativ einfach zu bewerkstelligen.

Bei den beiden Emulator-Vektoren handelt es sich um die Line A- und Line F-Vektoren. Wird ein nicht vorhandener Befehl abgearbeitet und die höchsten vier Bit enthalten die Kombinationen 1010 (hex. A) oder 1111 (hex. F), so werden diese beiden Vektoren angesprungen.

Der nicht initialisierte Interrupt-Vektor dient zum Erkennen unerwünschter Interrupts oder nicht initialisierten Interrupt-Vektor-Registern von Peripheriebausteinen.

Falls ein Busfehler während der Interruptquittierung auftritt, wird der unechte Interrupt-Vektor benutzt.

Nun zu den Interrupt-Autovektoren.

Wie oben schon erwähnt, besitzt der 68 000er sieben Interruptebenen, wobei die siebte die höchste Interruptebene ist. Diese Ebene ist der sogenannte „nicht maskierbare Interrupt“ (NMI).

Bild 1: Die Register des 68000

Durch Setzen bzw. Löschen der drei Interruptbits im Statusregister werden die einzelnen Ebenen ausgewählt. Bei den Autovektoren handelt es sich um Vektoren, bei denen der Prozessor sich aus der beteffenden Interruptebene die richtige Vektornummer ableitet. Als Gegenstück dazu liegen am Ende der Vektorenliste 6Adresse $00 - $3FC) die Non-Autovektoren, die vom Anwender erzeugt und über den Datenbus übergeben werden müssen.

Dem ST stehen allerdings nur die Ebenen 2, 4 und 6 zur Verfügung. Diese Vektoren zeigen auf die Horizontal/ Vertikal-Blank-Routinen und die vom MFP-Baustein verwalteten Interrupts.

Als letztes werden die TRAP-Vektoren besprochen. Sobald der Prozessor einen TRAP-Befehl abarbeitet, lädt er den betreffenden TRAP-Vektor in den Programmzähler und startet das an dieser Adresse stehende Programm. Beim ST werden allerdings nur vier von den 15 TRAP-Vektoren benutzt. So ruft TRAP #1 das GEMDOS, TRAP #2 das GEM, TRAP # 13 das BIOS und TRAP # 14 das XBIOS auf.

Die Register

Der 68 000er verfügt über acht 32 Bit-Datenregister, sieben 32 Bit-Adreßregister, zwei 23 Bit-Stackpointer, einen 32 Bit-Programmzähler und ein 16 Bit-Statusregister (siehe Bild 1).

Die acht Datenregister D0 - D7 sind vielseitig verwendbar. Sie können entweder als Datenregister im üblichen Sinne oder auch als Indexregister benutzt werden. Byte-Operanden belegen die Bits 0-7, Wort-Operanden 0 - 15 und Langwort-Operanden die vollen 23 Bits. Wenn das Datenregister als Quell- oder Ziel-Operand verwendet wird und das Datenformat nicht 32 Bit ist, dann wird nur der jeweils untere Teil des Registers geändert und der obere bleibt erhalten.

Auch die Adreßregister A0 - A6 bestehen aus je 32 Bit. Als Datenformate für Quell-Operanden sind allerdings nur Wort und Langwort zulässig. Wenn ein Adreßregister als Ziel dienen soll, werden in jedem Falle die ganzen 32 Bits verändert. Ist das Datenformat des Ziel-Operanden ein Wort, so wird er vorzeichenrichtig auf 32 Bit erweitert.

Die beiden Register A7 und A7’ sind ebenfalls Adreßregister und dienen dem Prozessor als Stackpointer. Das Register A7 ist der sogenannte Anwender-Stackpointer (USP). Er wird vom Prozessor zum Zugriff auf den Stack (Kellerspeicher) benutzt, solange er sich im Anwender-Modus befindet. Sobald er sich jedoch im Supervisor-Modus befindet, wird das Register A7’, der Supervisor-Stackpointer, eingesetzt. Dabei sei bemerkt, daß die beiden Register zwar unter den selben Namen angesprochen werden, aber physikalisch vollkommlen getrennt sind.

Der Programmzähler (PC) sei mehr oder wenig nur zur Ergänzung erwähnt. Er beinhaltet immer die nächste abzuarbeitende Adresse des laufenden Programms.

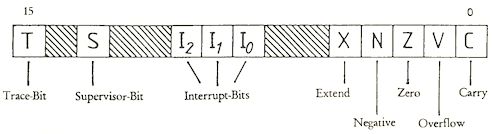

Doch nun zu dem fiir den Programmierer interessantesten Register, dem Statusregister (siehe Bild 2). Es ist beim 68 000er 16 Bit breit und wird in System-Byte (Bit 15-8) und Anwender-Byte (Bit 7-0) unterteilt. Das Anwender-Byte, auch unter dem Namen Codition Code Register (CCR) bekannt, enthält fünf Elags, die im folgenden beschrieben werden.

Das Carry-Flag C wird immer dann gesetzt, wenn bei einer arithmetischen Operation eine Eins als Übertrag entsteht.

Das OVerflow-Flag V wird immer dann gesetzt, wenn bei einer arithmetischen Operation eine Überschreitung des Zahlenbereichs stattgefunden hat.

Das Zero-Flag Z wird dann gesetzt, wenn bei einer arithmetischen Operation das Ergebnis gleich Null ist.

Das Negativ-Flag N wird dann gesetzt, sobald das Ergebnis einer arithmetischen Operation kleiner Null wird.

Das EXtend-Flag X wird ähnlich wie das Carry-Flag gesetzt. Allerdings beeinflussen nicht alle Befehle des 68 000 dieses Flag, so daß man je nach Verwendung der Befehle im Extend-Flag noch denselben Status haben kann wie vor einigen Operationen im Carry-Flag. Wann das Extend-Flag gesetzt wird, kann man aus unserer kleinen Befehlsübersicht ersehen.

Die übrigen Bits 5 — 7 sind nicht benutzt.

Im System-Byte werden ebenfalls nur fünf Bits verwendet. Da wären zunächst einmal die Bits 8 - 10. Bei ihnen handelt es sich um die drei Interrupt-Flags. Sie werden, je nachdem, welche Interruptebene man wünscht, gesetzt. Wie oben bereits gesagt, gibt es sieben Interruptebenen, was sich daraus ergibt, daß man mit drei Bit maximal eine Sieben (binär =111) darstellen kann.

Die anderen beiden Bits zeigen an, ob der Supervisor- (Bit 13) und der Trace-Modus (Bit 15) eingeschaltet sind. Auf den Trace-Modus sind wir ja schon oben eingegangen. Doch der Begriff Supervisor-Modus steht bis jetzt noch ungeklärt im Raum. Um es einfach auszudrücken: der Unterschied zwischen dem Supervisor- und dem Anwender-Modus besteht darin, daß im Supervisor-Modus alle Befehle benutzt werden dürfen, im Anwender-Modus dagegen alle, bis auf die privili-gierten Befehle, die in unserer Liste mit einem „Priv“ versehen wurden. Versucht man trotzdem, diese im Anwender-Modus zu benutzen, wird automatisch eine Ausnahmebehandlung (Privilegverletzung) ausgelöst. Die Unterscheidung zwischen den beiden Modi wurde deswegen gemacht, weil in einem eventuellen Mehrbenutzer-System nicht jeder Anwender auf alle Teile des Betriebssystems freien Zugriff haben soll. Nach einem RESET befindet sich der Rechner immer im Supervisor-Modus.

Bild 2: Das Statusregister des 68000

Die Adressierungsarten

Bevor wir zu den Adressierungsarten kommen, müssen wir noch kurz klären, was effektive Adressen (EA) sind. Bei den meisten Befehlen wird die Adresse des Operanden durch das effektive Adreßfeld im Operationscode bestimmt. In diesem Adreßfeld ist die effektive Adresse enthalten. Sie besteht aus zwei Hälften, dem Modusfeld und dem Registerfeld, wobei das Modusfeld die Adressierungsart und das Registerfeld die Nummer des gewählten Registers bestimmt.

Der 68 000er bietet die Möglichkeit, 13 verschiedene Adressierungsarten zu verwenden. Diese lassen sich dann wieder in fünf Hauptgruppen einteilen.

Gruppe 1: Register direkt

Wenn diese Adressierungsart gewählt wird, muß der Operand in einem der 16 Daten- und Adreßregister abgelegt sein.

Datenregister direkt DN

Adreßregister direkt An

Gruppe 2: Register indirekt

Bei dieser Adressierungsart ist der Operand im Speicher abgelegt. Seine Adresse ist in dem Register enthalten, das im Registerfeld der EA steht.

Adreßregister indirekt (An)

Adreßregister indirekt

mit Postinkrement (An) +

Adreßregister indirekt

mit Preinkrement -(An)

Adreßregister indirekt

mit Adreßdistanz dl6(An)

Adreßregister indirekt

mit Index und Adreßdistanz d8(An,Rx)

Gruppe 3: Daten absolut

Das Registerfeld in der EA wird in diesem Falle zur Bestimmung der speziellen Adressierungsart verwendet.

Absolute kurze Adresse $XXXX

Absolute lange Adresse SXXXXXXXX

Gruppe 4: Relativ zu Programmzähler

Programmzähler

mit Adreßdistanz dl6(PC)

Programmzähler

mit Index und Adreßdistanz d8(PC,Rx)

Gruppe 5: Daten unmittelbar

Bei dieser Adressierungsart sind die Daten im nächsten Wort bzw. den beiden nächsten Worten oder bereits direkt im Operationscode untergebracht.

Unmittelbar

#X, #XX, #XXXX oder

#XXXXXXXX

Unmittelbar schnell

#X, #XX, #XXXX oder

#XXXXXXXX

Kurze Assembler-Befehlsliste

In der Liste werden folgende Abkürzungen verwendet:

Operationen

An = Adreßregister n

C = Carry-Flag

CC = Carry-Flag gelöscht

CCR = Anwender-Byte des Statusregisters

Dn = Datenregister n

ea = effektive Adresse

Priv = privilegierter Befehl

Q = Quelloperand

Rx = Register x

Ry = Register y

SP = Stackpointer

SR = Statusregister

SSP = Supervisor-Stackpointer

USP = Anwender-Stackpointer

V = Overflow-Flag

X = Extend-Flag

Z = Zieloperand

Flaggen

✭ = Flag wird beeinflußt

- = Flag wird nicht beeinflußt 0 = Flag wird gelöscht U = Flag ist unbestimmbar

| Mnemonic | Beschreibung | Operation | Flaggen X N Z V C |

| ABCD | Addiere dezimal mit Carry | <Z)+<Q)+X = Z | * U * U * |

| ADD | Addiere binir | (Z)+(Q) = Z | ***** |

| ADDA | Addiere Adresse | (Z)+(Q) = Z | |

| ADDI | Addiere unmittelbar | (Z)+Daten = Z | ***** |

| ADDQ | Addiere schnell | (Z)+Daten = Z | ***** |

| ADDX Addiere mit Carry 2. Subtraktions-Befehle: | (Z)+(Q) = Z | ***** | |

| SBCD | Subtrahiere dezimal mit Carry | <Z)-<Q)-X = Z | * u * u * |

| SUB | Subtrahiere binir | (Z)-(Q) = Z | ***** |

| SUBA | Subtrahiere Adresse | (Z)-(Q) = Z | |

| SUBI | Subtrahiere unmittelbar | (Z)-Daten = Z | ***** |

| SUBQ | Subtrahiere schnell | (Z)-Daten = Z | ***** |

| SUBX Subtrahiere mit Carry 3. MultiDlikations-Befehle: | (Z)-(Q)-X = Z | ***** | |

| MULS | Multiplikation mit Vorze ichen | (Z)*(Q) = Z | - * * 0 0 |

| MULU 4. Divisions | Multiplikation ohne Vorze ichen -Befehle: | (Z)*(Q) = Z | - * * 0 0 |

| DI VS | Division mit Vorzeichen | (Z)/(Q) = Z | - * * * 0 |

| DI VU 5. Neaations | Division ohne Vorzeichen -. Clean— und Erweiterunas- | (Z)/(Q) = Z Befehle: | - * * * 0 |

| NBCD | Negiere dezimal mit Carry | 0-<Z)DEZ-X = Z | * u * u * |

| NEG | Negiere | 0-(Z) = Z | ***** |

| NEGX | Negiere mit Carry | 0-(Z)-X = Z | ***** |

| CLR | Lösche einen Operanden | 0->Z | - 0 1 0 0 |

| EXT 6. Logische- | Vorzeichenerweiterung Befehle: | (Z)vorzeichenerweitert — >Z | - * * 0 0 |

| AND | Logisches UND | (Z)&(Q) = Z | - * * 0 0 |

| ANDI | Logisches UND unmittelbar | <Z)& Daten = Z | - * * 0 0 |

| EOR | Logisches EXOR | (Z)#(Q) = Z | - * * 0 0 |

| EORI | Logisches EXOR unmittelbar | (ZDaten = Z | - * * 0 0 |

| NOT | E iner-Komplement | <Z>* = Z | -**00 |

| OR | Logisches ODER | (Z)$(Q) = Z | -**00 |

| ORI | Logisches ODER unmittelbar (Z)$ Daten = Z | -**00 | |

| ASL | Arithmetisches Linksven— sch ieben | X,C<-(-Z-)<-0 | ***** |

| Mnemonlc | Beschre ibung | Operation | X | Flaggen N Z V C | |||

| ASR | Arithmetisches Rechtsver— sch ieben | -X-Z-)->C,X <--- | * | * | * | * | * |

| LSL | Logisches Linksvei— sch ieben | X,C<-(-Z-X-0 | * | * | * | 0 | * |

| LSR | Logisches Rechtsver-sch ieben | 0-X-Z-)->C,X | * | * | * | 0 | * |

| ROL | Rundverschieben Links ohne Carry | C<- ( -Z- X--------> | - | * | * | 0 | * |

| ROR | Rundverschieben Rechts ohne Carry | -X-z-)->C <------- | - | * | * | 0 | * |

| ROXL | Rundverschieben Links mit Carry | <-X,C<-(-Z-X--------------> | * | * | * | 0 | * |

| ROXR 8. Comoare- | Rundverschieben Rechts mit Carry und Test-Befehle: | -X-z- )->C, x-> <------------- | * | * | * | 0 | * |

| CHK | Prüfe Register auf Grenzen | Wenn Dn<0 oder DnXea) => TRAP | - | * | U | u | u |

| CMP | Vergle iche | (Z)-CQ) | - | * | * | * | * |

| CMPA | Vergleiche Adresse | (Z)-(Q) | - | * | * | * | * |

| CMPI | Vergleiche unmittelbar | <Z1- Daten | - | * | * | * | * |

| CMPM | Vergleiche Speicher | (Z)-(Q) | - | * | * | * | * |

| TAS | Prüfe und setze Operanden | <Z) testen => CC l->7 des Ziels | - | * | * | 0 | 0 |

| TST 9. Bit-Befei | Prüfe einen Operanden tilg; | <Z) testen ->CC | - | * | * | 0 | 0 |

| BCHG | Prüfe ein Bit und Ändere es | - | - | * | - | - | |

| BCLR | Prüfe ein Bit und lösche es | - | - | * | - | - | |

| Mnemonlc | Beschre ibung | OperatIon | X | Flaggen N Z V | ||||

| BSET | Prüfe ein Bit und setze es | - | * | - | ||||

| BTST | Prüfe ein Bit | - | - | * | - | - | ||

| 10. Patentransport-Befehle; | ||||||||

| EXG | Vertausche Daten zwischen Reg i stern | Rx <—> Ry | ||||||

| LEA | Lade die effektive Adresse | Z->An | ||||||

| LINK | Anbinden und reservieren | An->SP-,SP->An SP+d->SP | ||||||

| MOVE | Transportiere Daten von der Quelle zum Ziel | <Q)->Z | - | * | * | 0 | 0 | |

| MOVE to CCR | Transportiere zum Bed ingungscode-Register | <Q)->CCR | * | * | * | * | * | |

| HOVE to SR | Transportiere zum Status-Reg ister | <Q)->SR | * | * | * | * | * | Pr i v |

| MOVE fron SR | Transportiere vom Status-Register | SR->Z | ||||||

| MOVE USP | Transportiere den Inhalt des Anwender—Stackpointers | USP->An An->USP | Pri v | |||||

| MOVEA | Transportiere Adresse | <Q)->Z | ||||||

| MOVEQ | Transportiere schnell | Daten ->Z | - | * | * | 0 | 0 | |

| MOVEM | Transport iere mehrere Reg ister | Register ->Z (Q)-> Register | ||||||

| MOVEP | Transportiere periphere Daten | (Q)->Z | ||||||

| PEA | Ablegen der effektiven Adresse | Z->SP- | ||||||

| SWAP | Vertausche Registerhälften | (R31-16X-XR15-0) | - | * | * | 0 | 0 | |

| UNLK | Lüsen | An->SP,SP+->An | ||||||

| 11. Bedingte Spränge und Operationen: | ||||||||

| Bcc | Verzweige bedingt | Wenn cc, dann PC+d->PC | ||||||

| DBcc | Prüfe Bedingung, dekrementiere und verzweige | Wenn cc=>Dn-1=Dn Dn<>-l=>PC+d->PC | ||||||

| Scc | Setze Byte bedingt | cc => Einsen->Z sonst Nullen->Z | ||||||

| “cc“ steht stellvertretend für alle anderen bedingten SprQnge (siehe auch Liste der Verzweigungsbedingungen.) | ||||||||

| 12. Unbedingte SprQnge: | ||||||||

| BRA | Verzweige immer | PC+d->PC | ||||||

| BSR | Verzweige zur Subroutine | PC->SP- PC+d->PC | ||||||

| JMP | Springe | Z->PC | ||||||

| JSR | Springe zur Subroutine | PC->SP- Z->PC | ||||||

| Mnemonic Beschreibung | Operation | Flaggen x n z v r. | |

| 13, | Rücksprünge: | ||

| RTE | Springe von Ausnahme zurück | SP+->SR SP+->PC | ***** Pr i v |

| RTR | Springe zurück und lade Bedingungscodes | SP+->CC SP+->PC | ***** |

| RTS | Springe zurück von der Subrout ine | SP+->PC | |

14 Trap-Befehle:

| ILLEGAL | Unzulässiger Befehl | PC-> SSP-, SR- > SSP-(Vektor)->PC | — — — — — |

| TRAP | Trap | PC->SSP-,SR-> SSP-<Vektor)->PC | - - - - - |

| TRAPV | Trap bei Überlauf | Wenn V, dann Trap |

15 Weitere Befehle:

| NOP | Keine Operation | ||

| RESET | Setze externe Einheiten zurück | - | ----- Pr i v |

| STOP | Lade das Status-Register und stoppe | Daten ->SR, Stop | *****Priv |

| Liste der Verzweigungsbedingungen | |

| BCC | Carry-Flag = 0 |

| BCS | Carry-Flag = 1 |

| BEQ | gleich, Zero-Flag = 1 |

| BGE | größer oder gleich |

| BGT | größer |

| BHI | höher |

| BLE | kleiner oder gleich |

| BLS | niedriger oder identisch |

| BLT | kle iner |

| BMI | Negativ-Flag = 1 |

| BNE | ungleich, Zero-Flag = 0 |

| BPL | Negativ-Flag = 0 |

| BVC | Overflow-Flag = 0 |

| BVS | Overflow-Flag = 1 |