Mit der Integration eines »DSP 56001« in den 68030-Computer »Falcon 030« will Atari — wie schon 1985 mit dem ersten ST-Computer — der Konkurrenz ein Schnippchen schlagen.

Der DSP 56001 im Pin-Grid-Array-Gehäuse

Der DSP 56001 im Pin-Grid-Array-Gehäuse

In der Gerüchteküche brodelt es schon lange, das Gerücht von Ataris neuem Supercomputer. Vielerlei Spekulation gab es jedoch über die Hardware, die Atari dem neuen Computer mitgeben wollte. Sollte es eine brandneue »68040«-CPU sein oder gar ein Parallelrechner werden? Nichts dergleichen. Keiner rechnete damit, daß sich Ataris Entwickler dazu entschlossen, einen DSP (Digital Signal Processor) von Motorola der 68030-CPU zur Seite zu stellen. Anders hätte sich die Fachwelt die Sound- und Grafikshow nicht erklären können, die der Falcon 030 auf der CeBIT-Pressekonferenz an den Tag legte.

Aus aktuellem Anlaß widmen wir also dem Zweitprozessor DSP 56001 von Motorola die folgenden Ausführungen.

Bei Echtzeitanwendungen oder besonders rechenintensiven Verfahren wie z.B. Fast Fourier Transformation (FFT), Faltung, Autokorrelation, rekursive Filter etc. gelangen die üblichen Prozessoren schnell an ihre Leistungsgrenzen.

Deshalb entwickelten die Chiphersteller spezielle Prozessoren, um die oben genannten Aufgaben zu lösen. Ein DSP unterscheidet sich nämlich in zwei wichtigen Punkten von den »normalen« Prozessoren:

- Durch die Forderung, viele Aufgaben in Echtzeit abzuarbeiten (Echtzeit bedeutet, daß der Prozessor so schnell rechnet, daß keine Eingangsdaten übersprungen werden), ist es notwendig, innerhalb des DSP von der »von Neumann«- zur »Harvard«-Architektur überzugehen. Im Klartext heißt dies, daß bestimmte Prozesse innerhalb des DSP auf mehreren Datenbussen zugleich ablaufen.

Somit kann der Prozessor eine Vielzahl von Befehlen oder Operationen in einem Zyklus abarbeiten. Dadurch, daß ein digitaler Signalprozessor auch noch einen umfangreichen Befehlssatz — ähnlich wie eine »normale« CPU — besitzt, ergeben sich universelle Einsatzmöglichkeiten.

- Normale Prozessoren bearbeiten Rechenaufgaben nur mit 16 oder 32 Bit Genauigkeit. Sind nun sehr viele arithmetische Operationen notwendig, so vergrößert sich natürlich auch der Rundungsfehler, der sich nach jeder arithmetischen Operation ergibt. Zwar läßt sich dieser Umstand durch Floating Point- oder Real-Arithmetik vermindern, doch steigt hierbei die Rechenzeit sprunghaft an. Der DSP 56001 besitzt deshalb für das Zwischenspeichern von Werten (Multiplikation) zwei 56 Bit große Register.

Gestatten: DSP 56001

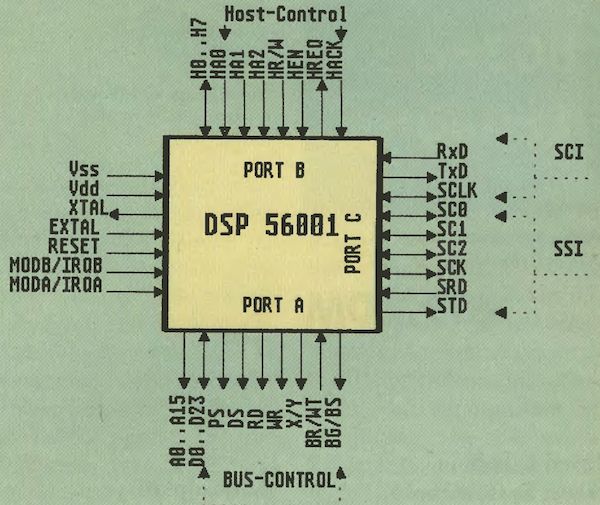

Verpackt ist der DSP 56001 in ein 88poliges (100 Pin bei SLAM-Gehäuse) Pin-Grid-Array-Gehäuse mit folgenden I/O-Funktionsgruppen (s. Abb. 2):

- Port A besteht aus Adreß- und Datenbus (24 Bit), mit dem sich andere DSPs oder MPUs im Master-slave-Betrieb an den DSP anbinden lassen. Des weiteren läßt sich diese Schnittstelle zur Einbindung des Prozessors in eine bestehende Computerhardware verwenden. Eine besonders einfache Integration erlauben hierbei die vorhandenen Kontrollein- und Ausgänge.

- Port B (Host Interface) ist ein Port, der sehr schnelle MPU, DSP bzw. DMA-Anwendungen erlaubt. Der Datenbus umfaßt hierbei 8 Bit und sieben zusätzliche Steuerleitungen. Über diese Schnittstelle läßt sich im übrigen auch ein normales externes 8-Bit-EPROM anschließen, um nach einem eventuellen Reset einen selbständigen Bootvorgang durchzuführen.

- Port C: Dieser Port läßt sich neben einer reinen 9-Bit-I/O-Anwendung in zwei Einheiten unterteilen, und zwar in eine asynchrone und in eine synchrone serielle Schnittstelle. Die asynchrone Schnittstelle (SCI) ist eine Art High-Speed-Modemschnittstelle mit 8 Bit und Full-Duplex-Betrieb. Sie besitzt die üblichen Steuerleitungen RxD, TxD und den erforderlichen Clock, so daß sich entweder direkt ein zweiter DSP anschließen oder aber mit geringer Zusatzhardware eine RS232-Schnittstelle nachbilden läßt. Die maximale Baudrate beträgt hierbei bei einer Clockfrequenz (des DSP) von 20,5 MHz ca. 320,00 KBaud.

Abb. 1: Die I/O-Gruppen des DSP 56001

Abb. 1: Die I/O-Gruppen des DSP 56001

Paralelverarbeitung

Das synchrone serielle Interface (SSI) hingegen ist eine sehr flexibel konfigurierbare Schnittstelle. Flexibel bedeutet hierbei, daß der Anwender mit einfacher Programmierung die Anzahl der Bits, das Protokoll, die Frequenz und die Synchronisation selbst bestimmen kann.

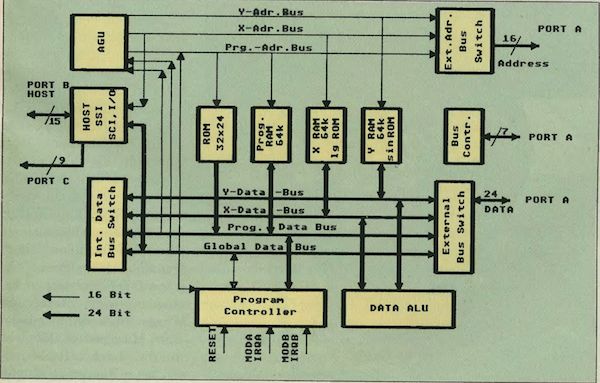

Wie bereits erwähnt, besitzt der DSP 56001 intern eine sogenannte Harvard-Architektur. Wie unsere Grafik (Abb. 3) zeigt, handelt es sich hierbei um die vier 24 Bit breiten bidirektionalen Datenbusse auf die der Prozessor parallel zugreifen kann.

Intern besitzt der frei programmierbare DSP drei verschiedene RAM- und zwei vorprogrammierte ROM-Bereiche. Bei den beiden letzteren handelt es sich um eine Logarithmus- und eine Sinuswertetabelle. Die drei wahlfreien Speicherbereiche gliedern sich wie folgt auf:

- Programm-RAM mit max. 64k externem Speicherbereich.

- X-RAM mit 64k RAM

- Y-RAM mit ebenfalls 64k RAM

Um die Geschwindigkeit zu verdeutlichen, die der Prozessor dem Falcon 030 verleihen könnte, geben wir hier einige Benchmarks des Prozessors aus dem Datenbuch DSP 56001 von Motorola an:

- 10,25 Millionen Instruktionen pro Sekunde.

- FFT (Fast Fourier Transformation) über 1024 Punkte' (komplex) in 3,23 ms für die 20,5-MHz-Version.

- 67 Tap FIR-Filter in 5,4 uS für die 27-MHz-Version.

Viel Rechenleistung sollte natürlich auch den entsprechenden Nutzen bringen. Wo liegen also die Anwendungsbereiche des DSP 56001 bzw. des Falcon 030?

Anwendungsvielfalt

Musikenthusiasten denken natürlich sofort an den »NeXT«, der ebenfalls einen DSP 56001 besitzt und dort als Synthesizer mit CD-Qualität seine Arbeit verrichtet. Ließen sich beispielsweise über eine sehr schnelle DSP-Schnittstelle, die der Falcon 030 wohl mit Sicherheit besitzt, (Musik-)Daten zum Computer übertragen, so ließen sich innerhalb des DSP bis zu 232 Ein-Zyklus-Be-fehle in Echtzeit abarbeiten, ohne die CD-Datenrate zu unterschreiten (errechnen läßt sich dieser Wert über die Taktfrequenz des DSP mit 20,5 MHz dividiert durch die Datenrate 44,1 kHz (CD) mal zwei [ein Zyklus benötigt zwei Takte]). Eine andere Anwendungsart ist die eines sehr schnellen Modems: Wie bereits bei der Beschreibung des Port C erwähnt, bietet der DSP erstaunliche Leistungsdaten für seine seriellen Schnittstellen.

Doch auch in der digitalen Bildverarbeitung, der Bildmustererkennung bzw. Grafikberechnung und Simulation, in der sehr viele Transformationsberechnungen notwendig sind, wird der DSP durch seine extrem kurze Rechenzeit für wahre Grafikwunder sorgen, die mit Sicherheit die Grafikfahigkeiten des TT um Größenordnungen übertreffen, (uw)

Abb. 2: Die internen Busleitungen des DSP

Abb. 2: Die internen Busleitungen des DSP