Ob Pilze, Bomben oder »unvorhergesehene Fälle« aller Art — jeder Benutzer ist bereits mit ihnen in Berührung gekommen« Diese ungemütlichen Gesellen stellen den einzig sichtbaren Teil eines intern ablaufenden Prozesses dar, der im Fachjargon »Exception« heißt.

Unabhängig von seinen Peripheriebausteinen kennt der MC 68000 drei unterschiedliche Betriebszustände. Im normalen Zustand läuft alles in geregelten Bahnen, d. h. der Prozessor arbeitet einzelne Befehle nacheinander ab. Tritt eine Exception (Ausnahme) auf, wechselt er sofort in den Supervisor-Modus. Exceptions treten bei Interrupts, dem Trap-Befehl oder bei aktivem Trace-Modus auf. Stolpert der Prozessor über einen doppelten Busfehler, ist er nicht in der Lage, diesen zu korrigieren, und stellt augenblicklich seine Arbeit ein. Dieser Zustand (Halt) läßt sich auch extern über die Halt-Leitung des Prozessors steuern.

Was genau ist eine Exception? Dazu ein Beispiel: Der MC 68000 erlaubt keinen Wort- oder Langwortzugriff auf ungerade Adressen. Der Befehl

move.l #12345678, $f8001

führt folglich zu einem Fehler. Damit der Prozessor weiß, wie er mit der Fehlerbehandlung fortfahren soll, gibt es ab der Speicheradresse $8 eine Tabelle mit sogenannten Exception-Vektoren. Diese Tabelle ist für alle Geräte, die einen 68000er benutzen, gleich und enthält für jede Exception eine Adresse, zu welcher der Prozessor verzweigt. Bei einem Adressfehler (s. o.) liegt dieser Vektor bei $0C. Das Programm an dieser Adresse kümmert sich um die Ausgabe der Bomben. Neben solchen Fehlern gibt es eine Reihe von Interrupts, Befehlen und Pseudo-Opcodes, die eine Exception auslösen (siehe Tabelle 2).

Bild 1. Bei einem Bus- oder Adreßfehler legt der Prozessor neben dem Programmzähler und dem Statusregister weitere vier Wörter ab

Bild 1. Bei einem Bus- oder Adreßfehler legt der Prozessor neben dem Programmzähler und dem Statusregister weitere vier Wörter ab

Innerhalb des Prozessors geschieht jedoch eine ganze Menge mehr. Je nach Art der Exception legt er eine Reihe von Informationen auf den Stack. Bei einer Exception aus Gruppe 2 und 3 sind dies nacheinander der Programmzähler sowie das Statusregister. Nach dem »LIFO«-Prinzip (»last in, first out«) befindet sich der Programmzähler nach diesem Vorgang in 2(sp). Dieser zeigt bei Trace und Interrupt auf den nächsten auszuführenden Befehl, bei allen anderen Exceptions der Gruppe 1 und 2 auf den durch die Exception abgebrochenen Befehl. Tritt ein Bus- oder Adreßfehler auf, wandern mehr Informationen auf den Stack (siehe Bild 1). Neben den erwähnten Informationen legt der Prozessor ein Super-Statuswort (vgl. Tabelle 1), die Zugriffsadresse und den Maschinencode des zuletzt abgearbeiteten Befehls auf den Stack.

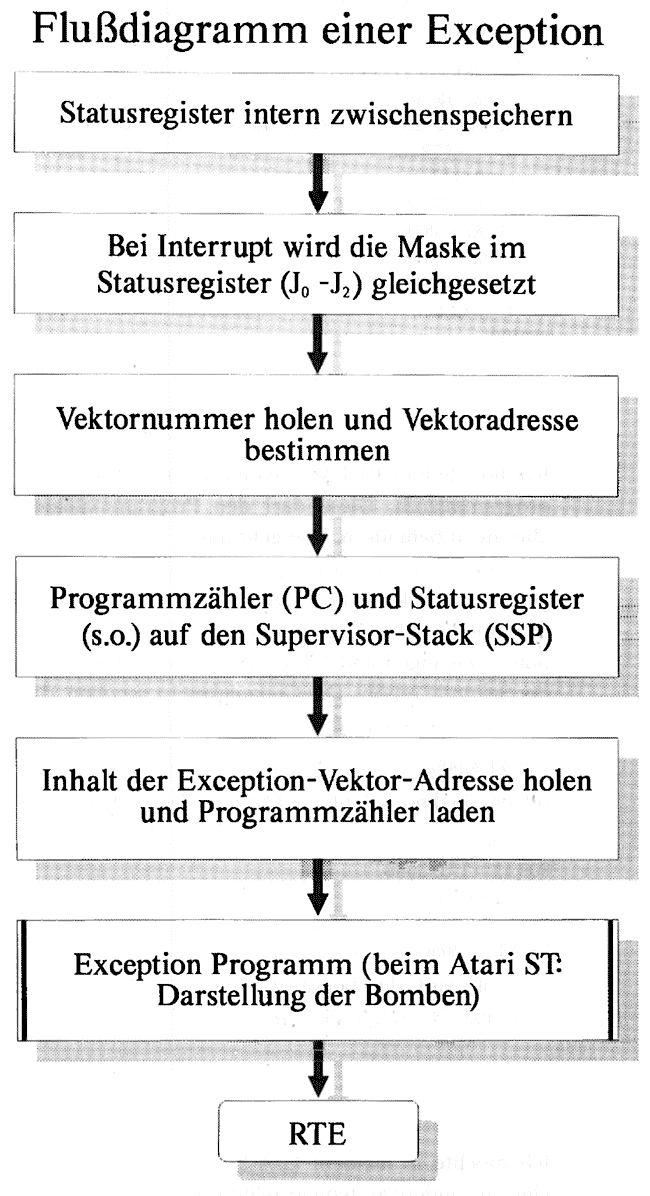

Bild 2. Tritt eine Exception auf, folgt der Prozessor stets dem gleichen Schema. Lediglich das Exception-Programm darf der Programmierer nach Belieben verändern.

Bild 2. Tritt eine Exception auf, folgt der Prozessor stets dem gleichen Schema. Lediglich das Exception-Programm darf der Programmierer nach Belieben verändern.

Bild 2 zeigt ein Flußdiagramm einer Exception. Zunächst sichert der Prozessor das Statusregister intern. War ein Interrupt Auslöser für eine Exception, wird die Interrupt-Maske im Statusregister angeglichen. Anhand der für jede Exception unterschiedlichen Vektornummer bestimmt der Prozessor die entsprechende Adresse in der Vektortabelle und rettet wie oben beschrieben wichtige Daten auf den Stack. Abschliessend lädt er den Programmzähler mit dem Inhalt der Vektor-Adresse und führt das an dieser Stelle befindliche Programm aus. Wichtig: Dieses Programm enthält als letzte Zeile den Befehl »RTE« (return from exception). Soll der unterbrochene Prozeß nach der Exception verlassen werden (z. B. bei Bus- oder Adreßfehlern), beendet die Funktion »Pterm0« das Exception-Programm. Als Anwendungsbeispiel finden Sie einen Mini-Debugger auf der TOS-Disk im Archiv »Buggy«. Dieses Programm ersetzt die TOS-interne Fehlerdarstellung (Bomben) und gibt weiterführende Informationen zum aufgetretenen Fehler.

Literatur: Jankowski, Reschke, Rabich - Atari ST Profibuch; Sybex; Hilf, Nausch - Die M68000 Familie Band 1; tewi

Tabelle 1. Das Super-Statuswort liegt nach einer Exception ganz oben auf dem Stack und enthält in den unteren fünf Bit nähere Informationen über den Auslöser.

| Bit |

Bedeutung |

| 0-2 |

Function-Code Leitungen (FC0-FC2) |

| 3 |

Ein Befehl oder eine Exception der Gruppe 1 oder 2 (Bit gesetzt) bzw. der Gruppe 3 (Bit gelöscht) wurde bei Abbruch verarbeitet |

| 4 |

Lesezyklus (Bit gesetzt) bzw. Schreibzyklus (Bit gelöscht) |

| Gruppe |

Exeption |

| 1 |

Reset Adress-Fehler Bus-Fehler |

| 2 |

Trace (Bit im Statusregister) Interrupt Opcodes ($Axxx,$Fxxx) Privilegverletzung |

| 3 |

TRAP, TRAPV, CHK, Division durch null |

Tabelle 2. Treten mehrere Exceptions gleichzeitig auf, entscheidet deren Priorität über die Reihenfolge der Ausführung. Gruppe 1 besitzt die höchste Priorität.